5G/NR Channel Codes Evolution Consideration and 3GPP Recommendation on Polar Codes. In order to meet higher data rates and more diverse requirements of typical NR scenarios including eMBB, mMTC, and URLLC, a powerful and flexible channel coding scheme is one of the fundamental components of the NR access technology. In the recent RAN1# discussion, various channel coding schemes were discussed and 3GPP considered convolutional codes, turbo codes, polar codes and LDPC codes for evaluation.

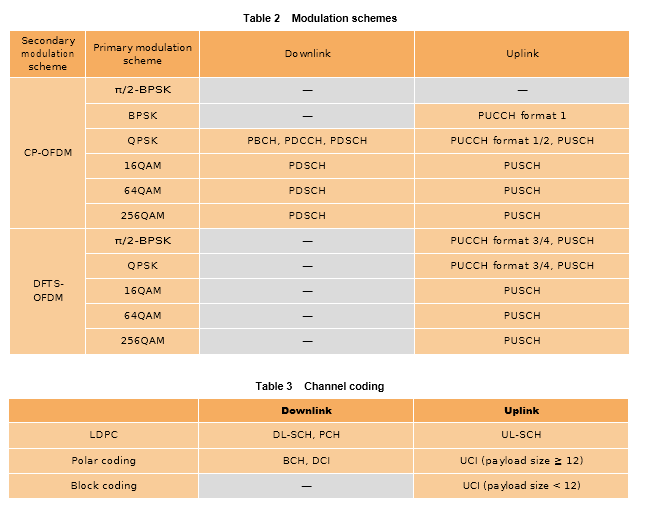

3GPP has adopted Polar Coding for 5G/NR Uplink/Downlink control channel for eMBB. To improve the performance of polar coding, concatenated coding and combined decoding schemes are proposed.

What is Polar Codes?

Polar codes can asymptotically (for code length going to infinity) achieve the capacity of any binary input symmetric memoryless channel with encoding and decoding complexity of the order O(N log N), where N is the code length. At present they are the only class of channel codes that are provably capacity achieving with an explicit construction.

Types of Polar Codes for 5G/NR

To improve the performance of Polar codes, some concatenated coding and combined decoding schemes are proposed.

- CRC-concatenated Polar codes (CA-Polar Code) with single-parity-check code concatenation and multi CRC-concatenation

- Parity-check concatenated Polar code (PC-Polar Code)

How Polar Codes Constructed?

A Polar code is constructed by recursively applying a linear polarization transform to the binary input symmetric and memoryless channel W, expressed as the 2-by-2 matrix. Repeated use of the transform, n = log2(N) times, results in an N-by-N matrix, denoting the n-fold Kronecker product. Polar codes leverage a phenomenon known as channel polarization. Above transform together with a successive cancellation decoder structure turns the N available channels (N channel uses) in to another set of N bit-channels, referred to as-synthesized channels, such that the capacities of these bit channels tend to 0 (fully unreliable) or to 1 (fully reliable) when N goes to infinity.

In fact, the proportion of reliable channels, K, tends to the capacity of the original communication channel. Data is communicated by placing information bits on the K reliable channels and placing fixed bits, usually zeros, on the N-Kunreliable channels. These bits on the unreliable channels are referred to as frozen bits, and the set of their positions is referred to as the frozen set F of size N-K. Frozen bits and the frozen set is known by both the encoder and the decoder. In this way, a polar code of code length N, information word length K, and code rate R=K/N is constructed.

- Polar code construction allows for different rates by the choice of the size of the frozen set F.

- It allows only for lengths that are powers of two, i.e., N = 2n.

- Polar codes of other lengths may be constructed by puncturing or shortening. In puncturing, some code bits are not transmitted, while in shortening, some systematic bits are set to zero and not transmitted.

Evolution Consideration of Different Channel Coding Schemes:

An advantage of the class of Polar Codes is that different types of decoders are possible for the same encoder. Therefore Polar codes are suitable to be used in a wide range of scenarios with diverse requirements. In contrast, other candidate schemes, such as Turbo codes, LDPC codes, and (TB)CCs cannot provide such flexibility. The power and area efficiency of Turbo decoders deteriorates very fast when increasing the block size. LDPC codes perform typically well for large blocks and high rates, however, performance is poor for rates below ½. It is noted that such code rate range can be the most common scenario in eMBB case. Table 1 summarizes the suitability of the different channel coding schemes. The gray squares indicate that the channel coding scheme cannot meet the requirements for that application.

| Polar Codes | Turbo Codes | LDPC | (TB)CC | |

| eMBB:Large Block >8K | Small-list decoder or SC decoder

Good power and area efficiency |

Low power/area efficiency; | Good power/area efficiency

Good performance only when code rate is higher than ½. |

Not considered |

| eMBB:1K~8K blocks

Fine granularity of code rates and code lengths |

Medium-List decoder;

Good performance for all code rates; Support any code rates and code lengths |

Good performance

Support a fine granularity of code rates and code lengths

|

Poor Performance for lower code rates lower than ½

Difficulty to support fine granularity of code rates and code lengths |

Not considered |

| URLLC/Control-CH/MTC-UL:Small block High-reliability | Large-List decoder;

Very good performance; Support very low code rate |

Poor performance with small block à not considered

Error Floor HARQ required for high-reliability |

Poor Performance with small block and low code rates

HARQ required for high-reliability |

VA decoder has poorer performance than SCL Polar

LVA decoder has much higher complexity than Polar List decoder. |

| MTC-DL:Small block Low Power | Small-list decoder or SC decoder for low-power realization | Poor Performance with small block à not considered | Poor Performance with small block à not considered | Viterbi Decoder for low-power realization;

Performance is worse than SCL decoder |

Furthermore, the performance of Polar Codes keeps improving along with increasing list size of the SCL decoder. According to our simulation with list sizes up to 2048, we have not observed any performance saturation so far. In contrast, we observe that the performance of turbo codes and LDPC codes saturates with the number of decoding iterations. As a result, the operators can keep improving the system capacity with newer ASIC technology. For example, when the list size is increased from 32 to 128 (the decoding complexity increases about by a factor of four), the BLER performance will gain another 0.5 ~0.7dB for some control channels. Therefore the system capacity can simply be increased with the availability of new Polar decoding chips.

Reference: R1-164039 and R1-1700979